- تاریخ انتشار : ۱۳۹۵

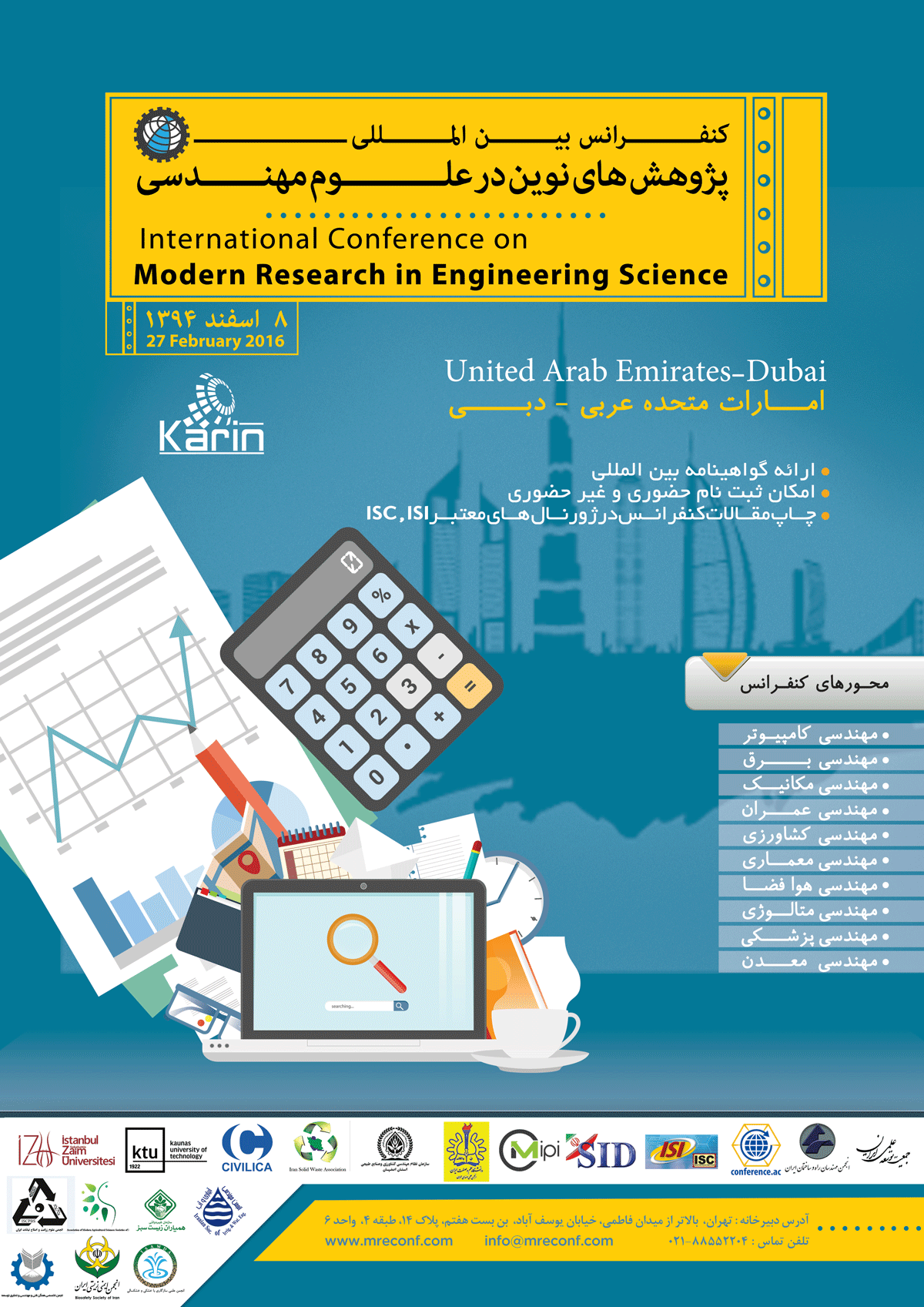

- ناشر : کنفرانس بین المللی پژوهش های نوین در علوم مهندسی

- زبان مقاله : همه

- تعداد صفحات : 9

- حجم فایل : 0 کیلوبایت

- نوع مقاله : مجموعه مقالات کنفرانس

- مجموعه : مهندسی و فناوری

چکیده مقاله

A candidate to acquire better performance and package density can be introduced as three-dimensional integrated circuits, which this is compared to traditional twodimensional. More specifically, a significant performance is obtained for 3D architectures through integrating schemes of Networks-on-Chip and advantages of 3D ICs. Since through-silicon-via (TSV) enables efficient inter-layer communication across multiple stacked layers, it has attracted a lot of interest. Two major architectures to employ TSVs as inter-layer communication channel in 3D architectures include router based and bus based organizations, i.e. the first deteriorates the performance at high injection rates and suffers from poor scalability and the second consumes more power. Wafer utilization and yield is reduced through area overhead of TSVs, found with a huge effect on designing 3D architectures with a large number of TSVs. The present research intends to reduce TSV footprint and power dissipation on each layer with a small performance penalty, for which a novel pipeline bus structure for interlayer communication is proposed to improve the performance by reducing the delay and complexity of traditional bus arbitration

نحوه استناد به مقاله

در صورتی که می خواهید به این مقاله در اثر پژوهشی خود ارجاع دهید، می توانید از متن زیر در بخش منابع و مراجع بهره بگیرید :

Mohammad Reza Hemmati.1؛Saeed Nasri.2؛Mehran Sedighi Doost.3؛ ۱۳۹۴، An investigation into Cluster-based topologies، کنفرانس بین المللی پژوهش های نوین در علوم مهندسی، https://scholar.conference.ac:443/index.php/download/file/2090-An-investigation-into-Cluster-based-topologies

در داخل متن نیز هر جا به عبارت و یا دستاوردی از این مقاله اشاره شود پس از ذکر مطلب، در داخل پرانتز، مشخصات زیر نوشته شود.

(Mohammad Reza Hemmati.1؛Saeed Nasri.2؛Mehran Sedighi Doost.3؛ ۱۳۹۴)